脉冲计数器的电路图设计(一)脉冲计数器的电路图,包括降压整流电路、光控脉冲发生器、计数电路、解码和显示电路。

脉冲计数器的电路图设计(二)如图所示,是计数器的一个例子,是对A端加入的脉冲进行累加计数的电路,一般用于对输入脉冲进行计数。S1到S4是用于设置计数的复位开关。当计数达到设定的计数时,负载电路动作,相应的继电器控制相关电路动作。如果将图5-12所示的时间脉冲加到A端,也可以构成一个基于工频的数字定时电路。

脉冲计数器的电路图设计(3)计数是最简单、最基本的运算,计数器是实现这种运算的逻辑电路。在数字系统中,计数器主要对脉冲数进行计数,以实现测量、计数和控制的功能,同时还具有分频功能。计数器由一个基本计数单元和一些控制门组成,计数单元由一系列具有存储信息功能的各种触发器组成,如rs触发器、T触发器、D触发器、JK触发器等。计数器广泛应用于数字系统中,如在电子计算机的控制器中计数指令地址以便按顺序取出下一条指令,在运算器中记录乘法和除法中加减的次数,在数字仪器中计数脉冲。计数器可以用来显示产品的工作状态,一般来说,它主要用来表示已经完成了多少份折页和配页工作。它的主要指标在于计数器的位数,一般是3位数和4位数。

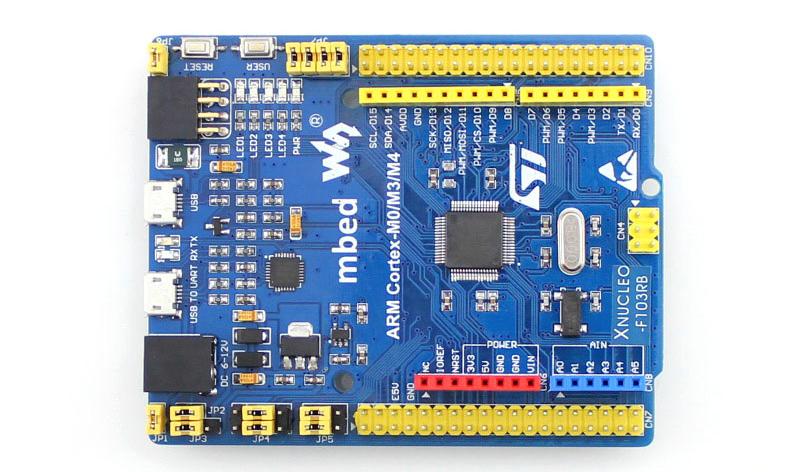

脉冲计数器的电路图设计(四)如图所示,原来的机械计数器只有两个磁开关信号端子,而电子计数器有C、D两个AC6.3V输入端子,共有四个接线端子。c1、 c2、 VD1、 VD 2构成倍压整流滤波电路。经7805稳压后,输出稳定的5V DC电压。被VD3、VD4降压后得到3.6V左右的DC电压,E1是小型3.6V镍镉充电电池,市电正常。当市电断电时,E1给负载供电,以保持断电时的计数值。VD3、VD4在这里起隔离作用。当A、B两端输入磁开关闭合时,220V交流电压接通,经R1 ~ R4降压,VD5~VD8桥整流,得到6V左右的DC脉动电压。经R5限幅后加到光电耦合器的发光管上使发光管点亮,光敏管的受光电阻降低,产生下降脉冲,经CD4011的N3反相后加到N: 010上。CD40110是一款“四合一电路”芯片,它将计数器、锁存器、解码器和笔段显示驱动器集成在同一基板上。当CD 40110的引脚5设置为高电平时,计数器复位。因此,K2是一个清除开关。9个引脚是递增计数输入,7个引脚是递减计数输入。整形后的计数脉冲从引脚9输入。当第一个CD40110计数到“9”时,如果输入另一个脉冲,引脚10输出一个进位脉冲。以此类推,总共可以测量“99999”个印数(最左边的数码管只显示零,没有计数功能)。

元器件选择:光耦OP1选择TLP532,或TLP332、TLP632等型号。为数字电路选择CD4011的型号。其他组件的标记如图所示。

脉冲计数器的电路图设计(5) CD4017是一个5位Johnson计数器,有10路解码输出和CP、CR、INH输入。时钟输入端的施密特触发器具有脉冲整形功能,对输入时钟脉冲的上升和下降时间没有限制。当INH为低电平时,计算器在时钟的上升沿计数;反之,计数功能无效。当CR为高电平时,计数器清零。约翰逊计数器提供快速操作,2输入解码选通和无毛刺解码输出。防锁门确保正确的计数顺序。解码输出通常为低电平,仅在相应的时钟周期内保持高电平。CO信号的进位每10个时钟输入周期完成一次,它被用作多级计数链的低脉动时钟。

CD4017的逻辑结构图

十进制计数器/分频器CD4017由计数器和解码器两部分组成,通过解码输出分配脉冲信号。整个输出序列是O0,O1、O2、.和O9相继出现与时钟同步的高电平,宽度等于时钟周期。

CD4017有十个输出(O0 ~ O9)和一个进位输出~ O5-9。每10个计数脉冲,~ O5-9可以得到一个进位正脉冲,进位输出信号可以作为下一级的时钟信号。

CD4017有三个输入(MR、CP0和CP0),其中MR作为清算终端。当电平或正脉冲加到MR端时,其输出O0为高,其它输出(O1 ~ O9)为低。CP0和~ ~CPl是两路时钟输入。如果上升沿用于计数,则信号从CP0输入。要按下降沿计数,信号从~ ~CPl端子输入。设置了两个时钟输入端,方便级联,可以驱动更多的二极管发光。

可以看出,当CD4017有连续脉冲输入时,其对应的输出端依次转为高电平,因此可以直接用作时序脉冲发生器。

CD4017和选择开关组成十进制计数器。

CD4017构成的1/n计数器电路图

由CD40171C构成的1/n计数器可分为两种情况:当n=10时,仅用一个CD4017IC和N个外部门电路就可构成1/n计数器,如图1-N所示,在时钟脉冲的作用下,CD4017IC一个接一个。计数当达到第Yn个解码输出时,由外部或非门组成的R-S触发器产生一个正脉冲输出,将CD40171C复位到零。如果n”=6,信号可以由进位输出端QCO输出;如果是n6,信号会由YO解码输出端输出,因为当是n6时,Q从端始终保持高电平(见CD4017的波形图),不会有脉冲跳变。

当分频系数n为n”10时,CD4017的位数要根据n的大小来确定,n=60时的电路工作原理如图1-12所示。当输入时钟脉冲中一位数输出YO为“1”,十位数输出Y6为“1”时,由外部门电路组成的R-S触发器产生正脉冲输出,从而清零各级计数器。当输入脉冲变为0电平时,CD4017的YO输出端再次复位R-S触发器,新一轮计数再次开始,得到连续的60分频脉冲输出。

用CD4017构成1 ~ 17位十进制计数器电路

脉冲计数器的电路图设计(六)在电路中,一个单脉冲发生器由两个与非门组成。74LS161计数器对单脉冲发生器产生的脉冲进行计数,计数结果送到字符解码器驱动七段数码管,使数码管显示单脉冲发生器产生了多少个脉冲信号。

74LS161计数器的级联使用:下图是74LS192组成的加法器级联使用进位输出控制上计数端的原理图: