CPLD和FPGA是我们经常使用的器件。有的说FPGA配芯片,CPLD没有;有人说FPGA逻辑资源最多,CPLD最少。有的不直接区分,都叫FPGA。那么这两者有什么区别呢?下面就以Altera公司的CPLD和FPGA为例,来谈谈两者的区别。

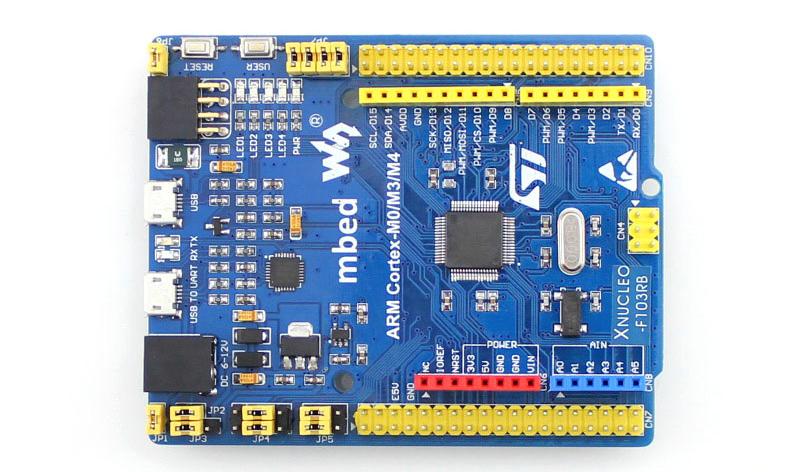

首先我们来看看CPLD的芯片结构,了解一下CPLD是由哪些部分组成的。下图是MAX系列CPLD的芯片结构图:

从图中可以清楚地看到,CPLD主要由三部分组成:宏单元、PIA和IO控制块。每个宏单元直接与GCLK(全局时钟)OE(输出使能)GCLR(清零)等控制信号相连,延时是一样的。宏单元还通过固定长度的金属线互连,这确保了逻辑电路的固定延迟。宏单元模块是CPLD的逻辑功能实现单元,是器件的基本单元,我们设计的逻辑电路就是由宏单元实现的。让我们来看看宏单元的具体结构:

一个宏单元主要由LAB局部阵列(逻辑阵列)、乘积项选择矩阵(乘积项选择矩阵)和一个可编程D触发器组成。其中逻辑阵列的每个交叉点可以通过编程打开以实现与逻辑,并且乘积项选择矩阵可以实现或逻辑。当这两部分协同工作时,就可以实现一个完整的组合逻辑。输出可以选择通过D触发器或旁路触发器。通过这种结构,我们可以发现CPLD非常适合实现组合逻辑,它还可以用后面的触发器实现一定的时序逻辑。

我们以cyclone系列为例来看看FPGA的内部结构:

FPGA内部主要由实验室单元、布线和IO单元组成。一个实验单元包含几个LE模块。LE模块是CycloneFPGA的基本逻辑单元。下图显示了LE模块的具体结构:

乍一看,似乎很复杂。事实上,最重要的部分是LUT查找表模块及其背后的D触发器。其他的是一些控制信号逻辑,比如清除进位旁路。也就是说,查找表是FPGA最基本的逻辑单元。Cyclone FPGA使用4输入LUT查找表。我们设计的逻辑电路都是通过EDA工具计算,然后存储在查找表中。每次根据输入信号查找对应的结果,然后输出。换句话说,FPGA的工作方式更像RAM,根据不同的输入信号(地址)输出相应的数据。

通过以上结构图的对比,我们可以清楚的看到,CPLD是由真实的组合电路组成的,FPGA归根结底是一个庞大的查找表!正是这种根本的区别,使得CPLD和FPGA在各方面都不一样。除了Altera,主要的CPLD和FPGA厂商还有Xilinx、Actel、Lattice和Atmel。每个公司的产品都有自己的特点,架构也会略有不同,但基本原理是一样的。我们来梳理一下CPLD和FPGA的主要区别:

CPLD的逻辑阵列更适合用可编程EEPROM或Flash技术实现。而FPGA显然更适合使用SRAM技术。

2)由于EEPROM或Flash技术的原因,CPLD在擦除次数上受到限制。但是在实际使用中,FPGA几乎可以说是没有配置数量限制的。

3)由于CPLD采用EEPROM或Flash技术,掉电后配置不会丢失,所以不需要插配置芯片。FPGA采用SRAM技术,掉电后配置会丢失,需要外接配置芯片。

4) CPLD更安全。因为配置芯片的原因,FPGA的安全性会比CPLD稍差。可以读取逻辑数据。(当然FPGA芯片会有一些加密措施。)

5) CPLD因为不需要上电重新配置,所以上电后可以立即工作。但是FPGA上电后需要配置时间,逻辑量的大小和配置方式的不同也会影响配置时间的长短。

6)由于CPLD的连续布线结构,其延时是均匀的、固定的。但是FPGA采用的分段布线结构导致延迟不固定。

7)由于工艺难度的差异,CPLD的集成度普遍较低,多在几千或几万门的芯片规模,很难做到几十万门。FPGA基于SRAM技术,集成度更高,可以轻松实现几十万甚至上百万门的芯片规模。最新的FPGA产品已经接近千万门的规模。

8)同样由于结构上的差异,CPLD更适合复杂的组合逻辑,比如编码和解码。FPGA更适合复杂的时序逻辑。换句话说,FPGA更适合触发器丰富的逻辑结构,CPLD适合触发器有限但乘积项丰富的逻辑结构。

9)同样由于工艺原因,一般CPLD的功耗比FPGA高。

当然,以上只是通常意义上的CPLD和FPGA的区别。技术在不断发展,这些差异不能一概而论。随着技术的发展,CPLD和FPGA也在不断更新。

Altera在Stratix III系列FPGA之后的产品中调整了LE的结构,如下图所示:

从原来的4输入查找表加D触发器到两个6输入查找表加两个D触发器。进一步细化查找表的结构图,如下所示:

6输入查找表可以细分为4输入查找表和两个3输入查找表。无论结构如何变化,基本的LUT查找表模式并没有改变,只是出于资源最优利用的考虑。但是,新的MAX II系列和MAX V系列CPLD从根本上模糊了CPLD和FPGA的区别。通过阅读芯片手册可以发现,虽然CPLD的两个系列名称没有改变,但架构与FPGA完全相同,最小单元也变成了LUT查找表,宏单元也不见了。或许和CPLD的关系是两个系列把配置电路集成到了芯片中,在实际使用中保持了和原来CPLD一样的使用习惯。可以说两个系列的产品已经是披着CPLD外衣的FPGA了。

从技术的延续性来看,可编程器件技术大致经历了PROM-PLA-PAL-GAL-EPLD-CPLD和FPGA的发展过程,CPLD和FPGA是两个不同的发展分支。制造商似乎正在模糊CPLD和FPGA之间的区别。也许未来只剩下名字的区别,两者统一成一种设备,或者出现更新的技术作为替代品。无论技术如何演进,作为工程师,我们要做的就是把握好每种设备的原理、优缺点和适用场景,然后在实际项目中正确选择和灵活使用。

1、我需要同时学习FPGA和CPLD吗?

很多同学对是否有必要同时学习FPGA和CPLD有疑问。阿东在这里说完全没有必要,以为FPGA和CPLD的设计语言都是Verilog。至于CPLD和FPGA的内部结构,在编码阶段是完全看不到的。软件会根据CPLD或者FPGA自动生成编程文件,建议学习的话学习FPGA。一旦FPGA学会了,你基本就会用CPLD了。

2、目前电路设计的规模越来越大,总是几万或者几十万甚至几百万个寄存器。在这个规模下,CPLD根本不会考虑,CPLD资源太少。