DDS是直接数字频率合成器的缩写,是一项关键的数字技术。与传统的频率合成器相比,DDS具有成本低、功耗低、分辨率高、转换时间快等优点。它广泛应用于电信和电子仪器领域,是实现设备全数字化的关键技术。

DDS芯片主要包括频率控制寄存器、高速相位累加器和正弦计算器(如Q2220)。频率控制寄存器可以以串行或并行方式加载并寄存用户输入的频率控制码;相位累加器根据dds频率控制码在每个时钟周期进行相位累加,得到相位值;正弦计算器计算相位值的数字正弦波幅度(芯片通常通过查表得到)。

DDS芯片的输出通常是数字正弦波,因此需要高速D/A转换器和低通滤波器才能得到可用的模拟频率信号。

DDS原理DDS技术是一种全新的频率合成方法,由JOSEPH TIERENY等人首先提出。它具有输出频率分辨率高、功耗低、频率切换速度快、频率切换时输出信号相位连续等特点。因此,了解用于数字信号处理的DDS模块及其硬件实现是非常重要的。

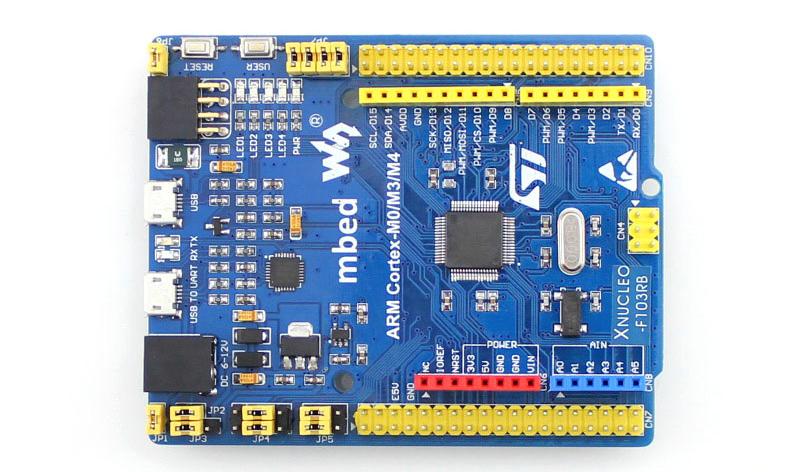

DDS的结构主要由四大结构组成:相位累加器、波形存储器、D/A转换器和低通滤波器。其结构框图如下:

图中,相位累加器由一个N位加法器和一个N位累加寄存器组成,是DDS模块中极其重要的部分。在参考频率时钟的驱动下,DDS模块开始工作;当每一个参考时钟到来时,累加器将频率控制字FW与寄存器输出的值累加,然后将累加的结果输入寄存器,累加寄存器将最后一个参考时钟作用时产生的数据反馈到累加器中。这样,在时钟的作用下,频率控制字可以不断累加。此时相位累加器输出的数据作为地址,通过在波形存储器中查找该地址对应的幅度表就可以完成相位到幅度的转换。

在DDS模块中,输出频率的公式为

输出信号的频率分辨率为

从上面两个表达式可以看出,当参考信号和加法器或寄存器的位数给定时,信号的最终输出频率主要由频率控制字决定。因此,当频率控制字改变时,输出频率也随之改变,从而实现调频的基本功能。