边界扫描是解决印刷电路板(PCB)上芯片间互连测试的一种方案。它与内部扫描明显不同。前者是在电路的输入/输出端口增加扫描单元并将这些扫描单元接入扫描通道,后者是将电路中的普通时序单元替换为具有扫描能力的时序单元并接入扫描通道。

一、边界扫描测试原理

边界扫描的原理是在核心逻辑电路的输入输出端口增加一个寄存器。通过连接这些I/O寄存器,数据可以串行输入到被测单元,并从相应的端口读出。在这个过程中,可以实现三个方面的测试。

首先是芯片级测试,即对芯片本身进行测试和调试,使芯片工作在正常的功能模式,通过输入端输入测试向量,通过观察串行移位的输出响应进行调试。

第二种是板级测试,检测集成电路和PCB之间的互连。其原理是将所有IC中的扫描寄存器与一个PCB上的边界扫描连接起来,通过一定的测试向量,可以发现元器件是否缺失或放错位置,同时可以检测出管脚的开路和短路故障。

最后,系统级测试,经过板级集成,可以通过在线编程CPLD或Flash在板上实现。

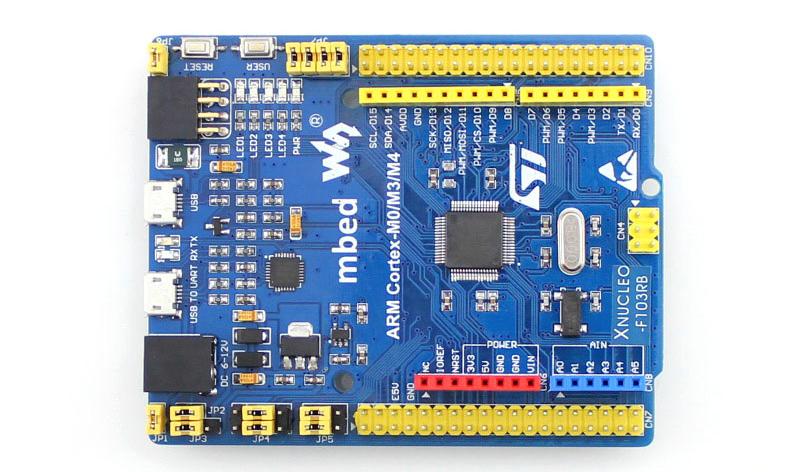

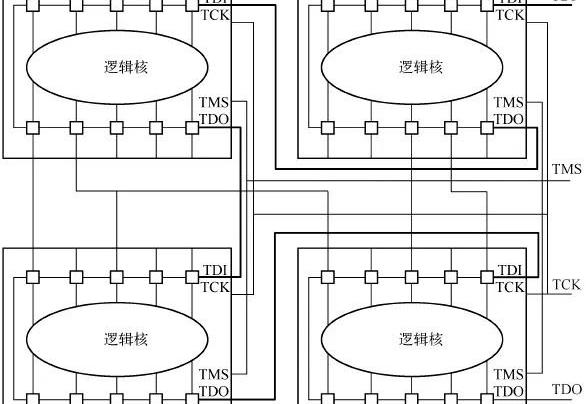

其中最重要的功能是测试板级芯片的互连,如图1所示。

图1基于边界扫描的板级互连测试

二、IEEE 1149.1标准

边界扫描(Boundary scan)是由一些欧美大公司联合成立的组织3354联合测试行动组(JTAG),是解决印刷电路板(PCB)上芯片间互连测试的解决方案。因为这个方案的合理性,1990年被IEEE采用,成为标准,即IEEE 1149.1。本标准规定了边界扫描的测试端口、测试结构和操作说明。

1.IEEE 1149.1结构

IEEE 1149.1的结构如图2所示,主要包括一个TAP控制器和一个寄存器组。其中,TAP控制器如图3所示;寄存器组包括边界扫描寄存器、旁路寄存器、标志寄存器和指令寄存器。主要端口是TCK、TMS、TDI和TDO,还有一个用户可选的端口TRST。

图2 IEEE 1149.1结构

图3 TAP控制器

2.端口定义如下

(1)TCK(测试时钟)

边界扫描设计中的测试时钟是独立的,与IC或PCB上的原时钟无关,原时钟也可以复用。

(2)TMS(测试模式选择)

因为测试过程中需要数据捕捉、移位、暂停等不同的工作模式,所以需要一个信号来控制。在IEEE 1149.1中,只有一个控制信号,工作模式由特定的输入序列决定,由有限状态机实现。该信号在测试时钟TCK的上升沿被采样。

(3)TDI(测试数据输入)

串行模式下有两种数据TDI输入。一个是指令信号,送到指令寄存器;另一个是测试数据(激励、输出响应等信号),输入到相应的边界扫描寄存器中。

(4)TDO(测试数据输出)

串行输出的数据也有两种,一种是从指令寄存器移位的指令,一种是从边界扫描寄存器移位的数据。

此外,还有一个可选的TRST端口,用于测试系统复位信号,并用于强制复位。

3.抽头控制器

TAP控制器的作用是对串行输入的TMS信号进行解码,使边界扫描系统进入相应的测试模式,并产生该模式下所需的所有控制信号。IEEE 1149.1的TAP控制器由有限状态机实现,状态转换图如图4所示。DR代表数据寄存器,IR代表指令寄存器。

图4 TAP控制器的状态转换图

4.寄存器组

(1)指令寄存器

如图5所示,指令寄存器由移位寄存器和锁存器组成,长度等于指令的长度。IR可以连接到TDI和TDO的两端,通过TDI串行输入指令,送到锁存器保存当前指令。这两部分都有一个解码单元,负责识别当前指令。由于JTAG有三个强制指令,该寄存器的宽度至少为2位。

图5指令寄存器

(2)旁路寄存器(BR)

旁路寄存器也可以直接连接到TDI和TDO的两端,并且仅由1位组成。如果PCB上有多个具有边界扫描设计的IC,则每个IC中的边界扫描链可以串联连接。如果此时有必要测试其中的一些IC,可以通过BYPASS指令绕过不需要测试的IC。如图6所示,如果需要测试Chip2和Chip3,可以在TDI输入110000处配置bypass寄存器,此时Chip1的bypass寄存器被置位,表示该芯片在测试过程中被旁路。

图6旁路寄存器示例

(3)身份登记册

如图7所示,在一般的边界扫描设计中,有一个固化了器件标识的寄存器,是一个32位的标准寄存器,其内容包含了器件的版本号、器件型号和制造商等信息,以便在PCB生产线上查看IC的型号和版本,进行维护和更换。

在器件标志寄存器的标准格式中,最低位(位0)为1,用于标识标志寄存器和旁路寄存器的标志位。第1到第11位数字是制造商的识别数字。根据国际联合电子器件工程委员会提出的建议,允许这11人拥有2032家厂商的标识。第12位到第27位代表设备的型号,总共可以代表216=65536种不同的型号。其余四位代表同一型号设备的不同版本。

图7标志寄存器

(4)边界扫描寄存器

边界扫描寄存器是边界扫描中最重要的结构单元,完成测试数据的输入、输出锁存和移位过程中必要的数据操作。它工作在多种模式下,首先,它满足扫描链上的串行移位模式,其次,它在正常模式下捕获并更新电路的数据,如图8所示。

图8边界扫描寄存器

边界扫描寄存器可以提供以下主要测试功能:

测试被测IC的外部电路,如可测试IC之间的互连,外部测试指令EXTEST此时可以使用;

使用INTEST进行被测电路的内部自测;

此时对输入输出信号的采样和更新不会影响核心逻辑电路的工作状态。

5.相关说明

JTAG规定了三个强制性指令:外部测试、旁路和采样/预加载。

(1)外部测试:外部测试说明

外部测试指令主要用于测试IC和PCB之间的连接或边界扫描设计之外的逻辑电路。执行该指令的主要操作是将测试向量串行移位到边界扫描寄存器,以模拟被测连接或外部逻辑电路,同时寄存器捕捉响应数据,并串行移出测试结果以供检查。

(2)旁路:旁路指令

这是由1组成的全1指令串。其功能是选择IC中的bypass寄存器BR,决定IC是否测试。

(3)采样/预加载:采样/预加载指令

采样指令用于在不影响核心逻辑正常工作的情况下,将边界扫描设计中并行输入端的信号捕获到边界扫描寄存器中,并在测试时通过采样指令捕获被测逻辑电路的响应。预加载指令的功能与采样基本相同,只是加载到边界扫描寄存器中的数据是程序员已知或确定的。除了上面提到的必要指令,JTAG还定义了一些可选指令:INTEST、IDCODE、RUNBIST、CLAMP和HIGHZ。

Intest是内部测试指令,用于测试核心逻辑电路。执行过程与外部测试指令基本相似,只是被测对象的位置刚好相反,其激励端和响应测试端良好且相反。

Idcode指令用于从标志寄存器中获取标志代码。

Runbist是一条运行自测指令,用于执行的自测功能

Clamp是一个分量指令,有两个作用,一是使bypass寄存器为0,二是使边界扫描寄存器BSR的输出为一组给定的固定电平。

Highz是一个输出高阻指令,可以使IC的所有输出端都处于高阻状态,即无效状态。

三、边界扫描测试策略和相关工具

1.板级测试策略

使用边界扫描IEEE 1149.1的板级测试策略分为以下三个步骤。

根据IEEE 1149.1标准建立边界扫描的测试结构。

利用边界扫描测试结构,对被测零件之间的连接进行矢量输入和响应分析。这是板级测试的主要环节,也是边界扫描结构的主要应用。可用于检测由电气、机械、温度等引起的板级集成故障。

测试单核逻辑可以初始化逻辑,利用自己的测试结构。

2.相关EDA工具

业界使用的主要边界扫描工具是Mentor的BSDArchitect和Synopsys的BSD编译器。以后者为例,主要设计流程如图9所示。该过程将生成BSDL文件,该文件是边界扫描测试描述文件。该文件的内容包括引脚定义和边界扫描链的组成结构。通用ATE可以识别这个文件,自动生成相应的测试程序,完成对板上芯片漏电流等参数的测试。

图9边界扫描设计流程