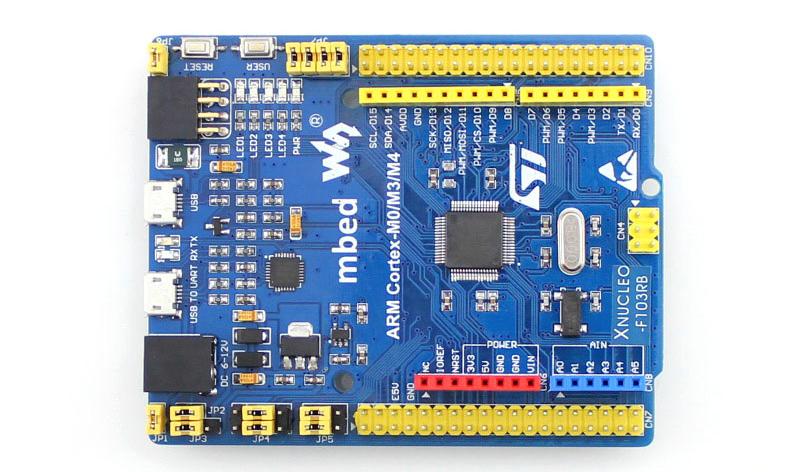

数字钟设计电路图(1)本设计主要采用中断方式,使用INT0和INT1中断,分别由按钮s1和s2触发。s1键用作功能选择键,当s1键被按下时,它可以在不同的功能之间切换。按s1从时钟状态进入秒表状态,再按一次,秒表开始计时,再按s1停止秒表,再按s1进入调时钟状态。每次按下它,您可以使用键s2来调整相应的位。复位电路具有上电自动复位和手动复位功能。P2控制三极管驱动数码管,P0口作为数据输出口。

数字钟设计电路图(二)“时”和“分”的校准电路是一样的。现在,用于“分钟”的校准电路被用来说明时间的校准。(www.t262.com)在正常定时期间,与非门U2D的一个输入为1。开启,使秒计数器输出的分脉冲加到U2D的另一个输入上,通过U1D进入分计数器。此时U3D关闭,因为一个输入端为0,用于校准的第二个脉冲无法进入。

在学校“阅卷”时按下开关J1,情况与上述情况相反。U2D关闭,U3D打开,标准秒脉冲直接进入分钟计数器进行快速“分钟”校准。同样,在校准“时间”时,按下开关,标准秒脉冲直接进入时间计数器,快速校准“时间”。可以看出,U1D、U2D和U3D构成了一个替代电路。

数字钟设计电路图(3)从图中可以看出,当“小时”位U8计数输入端接第10个触发信号时,U8计数器清零,进位端QD输出进位信号给U7“小时”十位计数器。当第24个“小时”(来自“分”计数器的进位信号)脉冲到达时,U8计数器的状态为“0100”,它们分别被送到U7和U8计数器的清零端R01和R02,并通过74LS290而不是13内部的R01和R02。

数字钟设计电路图(四)数字钟的计数电路由两个六进制计数电路和一个十进制计数电路实现。不过考虑到对74LS90的熟悉程度,感觉用两个74LS90分别控制秒和分的十位和一位。一个十进制数字和一个十六进制数字可以完美地解决六十进制的秒计数。然后用74ls191和74ls74分别控制1位和第10位。